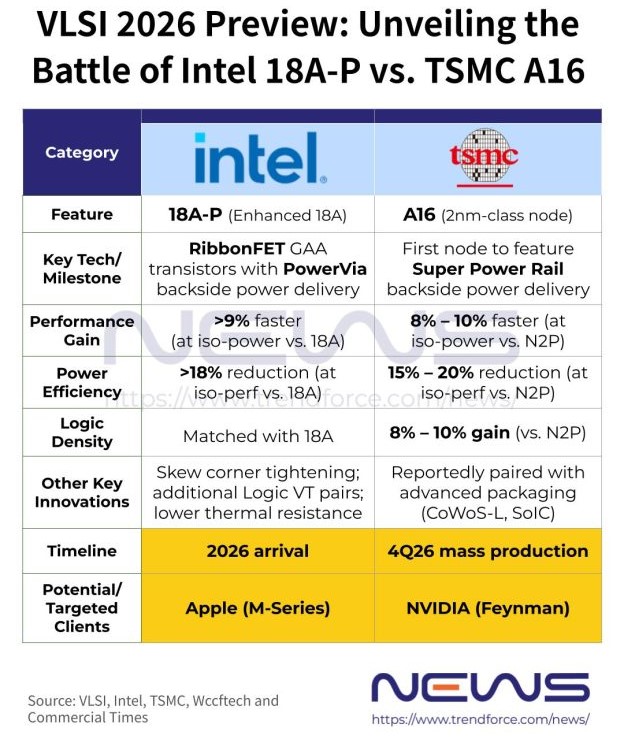

På denne baggrund er det kommende VLSI Symposium blevet en vigtig scene for konkurrence mellem Intel og TSMC inden for avanceret procesteknologi.TSMC forventes at præsentere sin 2nm-klasse A16 ångstrøm CMOS-teknologi ved begivenheden.Processen bruger gate-all-around- eller GAA-transistorer og introducerer bagsidestrømforsyning gennem et nyt "Super Power Rail" eller SPR-design.

Intel har allerede afsløret nogle kernedetaljer i sin 18A-P-proces.Ifølge medierapporter forbliver de vigtigste strukturelle parametre for 18A-P, herunder bibliotekshøjde og kontaktet polypitch, de samme som baseline 18A-processen.De vigtigste opgraderinger er fokuseret på tuning på transistorniveau og spændingsoptimering.Antallet af VT BT-parmuligheder er blevet udvidet fra fire i 18A til mere end fem, og en ny logisk tærskelspænding er blevet tilføjet mellem ultra-lav tærskelspænding eller ULVT og lav tærskelspænding eller LVT.

18A-P-processen forbedrer også procesvariabilitetskontrol og termisk effektivitet, hvilket understøtter dens laveffekt- og højtydende mål.Disse forbedringer er blandt årsagerne til, at Apple og andre fabelløse chipdesignere viser større interesse for teknologien.For at opnå disse præstationsgevinster har Intel introduceret nye RibbonFET-varianter baseret på dens gate-all-around-arkitektur, herunder forbedrede kontakt højtydende transistorer og optimerede laveffektenheder, hvilket styrker enhedsgrundlaget for bedre ydeevne og energieffektivitet.

Intel sagde også, at de har strammet de skæve hjørner af 18A-P-processen med 30 % med det formål at forbedre ydeevnekonsistensen og reducere variabiliteten.Skæve hjørner henviser til forskelle i transistorydelse og effektkarakteristika inden for den samme procesknude.Efterhånden som halvlederfremstilling udvikler sig til mere aggressive noder, bliver transistoradfærden mere og mere ujævn, hvilket gør variabilitetskontrol til en stor udfordring.

Intels første produkt baseret på 18A-processen, Panther Lake, gik angiveligt i volumenproduktion ved udgangen af 2025. Virksomheden planlægger at udrulle 18A-afledte procesteknologier i faser, hvor 18A-P forventes at ankomme i 2026 og en yderligere opgraderet 18A-PT-proces er planlagt til 2028.

I mellemtiden forbereder TSMC sig til debuten af sin A16-proces, virksomhedens første node baseret på Super Power Rail-teknologi.Processen vil blive formelt præsenteret på VLSI Symposium, der er planlagt til den 14. til 18. juni. Ifølge TSMC, sammenlignet med den præstationsforbedrede N2P-node, kan A16 levere en 8% til 10% ydeevneforbedring ved samme effekt, reducere strømforbruget med 15% til 20% ved samme ydeevne og give en ekstra 1 den% 8% stigning i chip.

TSMC planlægger at påbegynde masseproduktion af A16 i fjerde kvartal af 2026. Brancherygter tyder bredt på, at Nvidias Feynman-chip kan være det første produkt, der tager processen i brug.Forsyningskædekilder indikerer, at A16 vil blive parret med CoWoS-L og SoIC avancerede pakketeknologier, hvilket muliggør systemskalering på op til 9,5 gange sigtekorsstørrelsen.Processen er hovedsageligt rettet mod højtydende computing, eller HPC, arbejdsbelastninger.